# Errata AM65x Processors Silicon Revision 2.1, 2.0, 1.0

#### ABSTRACT

This document describes the known exceptions to the functional specifications (advisories). This document may also contain usage notes. Usage notes describe situations where the device's behavior may not match presumed or documented behavior. This may include behaviors that affect device performance or functional correctness.

# **Table of Contents**

| 1 Usage Notes and Advisories Matrices                              | 2 |

|--------------------------------------------------------------------|---|

| 2 Nomenclature, Package Symbolization, and Revision Identification |   |

| 3 Silicon Revision 2.1, 2.0, 1.0 Usage Notes and Advisories        |   |

| Revision History                                                   |   |

| ··· · · · · · · · · · · · · · · · · ·                              |   |

# **1 Usage Notes and Advisories Matrices**

Table 1-1 lists all usage notes and the applicable silicon revision(s). Advisories Matrix lists all advisories, modules affected, and the applicable silicon revision(s).

|       |                                                                                                  | SILICON | <b>REVISIONS AI</b> | FFECTED |

|-------|--------------------------------------------------------------------------------------------------|---------|---------------------|---------|

| ID    | DESCRIPTION                                                                                      | AM65x   |                     |         |

|       |                                                                                                  | 2.1     | 2.0                 | 1.0     |

| i2033 | Section 3.1.1 — Fail-Safe IO's: Latch-up Risk on Fail-Safe IOs                                   | Yes     | Yes                 | Yes     |

| i2082 | Section 3.1.2 — ADC: High Input Leakage Current May Impact ADC Accuracy                          |         |                     | Yes     |

| i2007 | Section 3.1.3 — INTRTR: Spurious Interrupts Generated when Programming Certain Interrupt Routers | Yes     | Yes                 | Yes     |

| i2351 | Section 3.1.4 — OSPI: Controller does not support Continuous Read mode with<br>NAND Flash        | Yes     | Yes                 | Yes     |

#### Table 1-1. Usage Notes Matrix

#### **Advisories Matrix**

|              |                                                                                                                                      |     | SILICON REVISIONS AFFECTED AM65x |     |  |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------------|-----|--|

| MODULE       | DESCRIPTION                                                                                                                          |     |                                  |     |  |

|              |                                                                                                                                      | 2.1 | 2.0                              | 1.0 |  |

| ADC          | i2151 — ADC: Debounce time control register                                                                                          |     | Yes                              | Yes |  |

| Boot, USB3SS | i2019 — Boot, USB3SS: Boot ROM Does Not Support USB Host MSC (Mass Storage Class) Boot Mode                                          |     |                                  | Yes |  |

|              | i2020 — Boot, USB3SS: Boot ROM Does Not Support USB Device Firmware Upgrade (DFU) Boot Mode                                          |     |                                  | Yes |  |

| Boot, UART   | i2030 — Boot, UART: UART Boot Mode Never Times Out                                                                                   |     |                                  | Yes |  |

| Boot         | i2038 — Boot: FAT16 Fails When Root Block Resides in More Than One Cluster                                                           | Yes | Yes                              | Yes |  |

|              | i2307 — Boot: ROM does not properly select OSPI clocking modes based on BOOTMODE                                                     | Yes | Yes                              | Yes |  |

|              | i2328 — Boot: USB MSC boots intermittently                                                                                           | Yes | Yes                              | Yes |  |

|              | i2371 — Boot: ROM code may hang in UART boot mode during data transfer                                                               | Yes | Yes                              | Yes |  |

| CBASS        | i2207 — CBASS: Command Arbitration Blocking                                                                                          | Yes | Yes                              | Yes |  |

| CC_ARMSS     | i2069 — CC_ARMSS: Powering Down CC_ARMSS1 Causes System Data Corruption                                                              |     |                                  | Yes |  |

| Cortex-R5F   | i2099 — Cortex-R5F: Deadlock Might Occur When One or More MPU Regions is<br>Configured for Write Allocate Mode                       | Yes | Yes                              | Yes |  |

|              | i2129 — Cortex-R5F: High Priority Interrupt is Missed by VIM                                                                         | Yes | Yes                              | Yes |  |

|              | i2132 — Cortex-R5F: Interrupt Preemption (Nesting) is Unavailable if Using VIM Vector<br>Interface for Interrupt Handling            | Yes | Yes                              | Yes |  |

| CPSW         | i2027 — CPSW: CPSW does not support CPPI receive checksum (Host to Ethernet) offload feature                                         |     |                                  | Yes |  |

|              | i2084 — CPSW: CPSW Does Not Support Intersperced Express Traffic (IET – P802.3br/<br>D2.0) In 10/100Mbps Mode                        |     |                                  | Yes |  |

|              | i2139 — CPSW: ALE Incorrectly Routes Packets With CRC Errors                                                                         |     |                                  | Yes |  |

|              | i2148 — CPSW: CPSW Directed Frames are Not Observed When Classification Overrides the Destination Port Via the Egress Opcode Feature | Yes | Yes                              | Yes |  |

|              | i2184 — CPSW: IET express traffic policing issue                                                                                     | Yes | Yes                              | Yes |  |

|              | i2185 — CPSW: Policer color marking issue                                                                                            | Yes | Yes                              | Yes |  |

| CPTS         | i2083 — CPTS: GENF (and ESTF) Reconfiguration Issue                                                                                  |     |                                  | Yes |  |

|              | i2141 — CPTS: GENF and ESTF Nudge Value Not Cleared by Hardware                                                                      | Yes | Yes                              | Yes |  |

| CSI          | i2204 — CSI: Interface Setup/Hold Timing Does Not Meet MIPI DPHY Spec above 600MHz                                                   | Yes | Yes                              | Yes |  |

| DCC          | i2018 — DCC: Incorrect Counter Values in DCC Operation                                                                               |     |                                  | Yes |  |

|              | i2073 — DCC: Suspend Mode Not Functional                                                                                             |     |                                  | Yes |  |

| DDR          | i2231 — DDR: LPDDR4 and DDR3L are not supported                                                                                      | Yes | Yes                              | Yes |  |

|              | i2262 — DDR: Mode Register write busy indicator not cleared after completing software-<br>driven mode register access                | Yes | Yes                              | Yes |  |

|              | i2264 — DDR: Timing violation from read/write command to Software-Initiated MRW command (LPDDR4 only)                                | Yes | Yes                              | Yes |  |

|              | i2265 — DDR: Issuing MRR/MRW commands in self-refresh state (LPDDR4 only)                                                            | Yes | Yes                              | Yes |  |

|              | i2266 — DDR: Controller derating logic does not consider system temperature when derating is enabled (LPDDR4 only)                   | Yes | Yes                              | Yes |  |

2

Texas

**STRUMENTS**

www.ti.com

|               |                                                                                                                                                                                           |     | SILICON REVISIONS AFFECTED |     |  |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|-----|--|

| MODULE        | DESCRIPTION                                                                                                                                                                               |     | AM65x                      |     |  |

|               |                                                                                                                                                                                           | 2.1 | 2.0                        | 1.0 |  |

|               | i2268 — DDR: Controller can violate timing from Self-Refresh Exit (SRX) to Power-Down Entry (PDE) for DDR3                                                                                | Yes | Yes                        | Yes |  |

| DDRSS         | i2009 — DDRSS: DDR Controller ECC Scrubbing Feature Can Cause DRAM Data Corruption                                                                                                        | Yes | Yes                        | Yes |  |

|               | i2022 — DDRSS: Independent Impedance Control for Address/Control and Data Bus Lanes is Not Available                                                                                      |     |                            | Yes |  |

| DMSC          | i2245 — DMSC: Firewall Region requires specific configuration                                                                                                                             | Yes | Yes                        | Yes |  |

| DRU           | i2198 — DRU, UTC: Issue with setting ICNT3 to 0 when not being used                                                                                                                       | Yes | Yes                        | Yes |  |

| DSS           | i2000 — DSS: DSS Does Not Support YUV Pixel Data Formats                                                                                                                                  |     |                            | Yes |  |

|               | i2032 — DSS: DSS DPI Interface does not support BT.656 and BT.1120 output modes                                                                                                           |     |                            | Yes |  |

|               | i2039 — DSS: Frame Buffer Flip/Mirror Feature Using RGB24/BGR24 Packed Format Can Result in Pixel Corruption                                                                              | Yes | Yes                        | Yes |  |

|               | i2097 — DSS: Disabling a Layer Connected to Overlay May Result in Synclost During the Next Frame                                                                                          | Yes | Yes                        | Yes |  |

| GIC           | i2101 — GIC: ITS Misbehavior                                                                                                                                                              |     |                            | Yes |  |

| HyperFlash    | i2119 — HyperFlash: HyperFlash is Not Supported                                                                                                                                           | Yes | Yes                        | Yes |  |

| A             | i2196 — IA: Potential deadlock scenarios in IA                                                                                                                                            | Yes | Yes                        | Yes |  |

| IO, MMCSD     | i2025 — IO, MMCSD: Incorrect IO Power Supply Connectivity Prevents Dynamic Voltage Change on VDDSHV6 and VDDSHV7                                                                          |     |                            | Yes |  |

| MCAN          | i939 — MCAN: Message Transmitted with Wrong Arbitration and Control Fields (Early Start of Frame)                                                                                         | Yes | Yes                        | Yes |  |

|               | i2278 — MCAN: Message Transmit order not guaranteed from dedicated Tx Buffers configured with same Message ID                                                                             | Yes | Yes                        | Yes |  |

|               | i2279 — MCAN: Specification Update for dedicated Tx Buffers and Tx Queues configured with same Message ID                                                                                 | Yes | Yes                        | Yes |  |

| MCU           | i2173 — MCU: MCU domain may hang if main domain is issued a reset                                                                                                                         |     | Yes                        | Yes |  |

| MDIO          | i2329 — MDIO: MDIO interface corruption (CPSW and PRU-ICSS)                                                                                                                               |     | Yes                        | Yes |  |

| MMCSD         | i2024 — MMCSD: MMCSD Peripherals Do Not Support HS400                                                                                                                                     | Yes | Yes                        | Yes |  |

|               | i2026 — MMCSD: Negative Current from UHS-I PHY May Create an Over-Voltage<br>Condition on VDDS6 and VDDS7 Which Exposes the Device to a Significant Reliability<br>Risk                   |     |                            | Yes |  |

|               | i2312 — MMCSD: HS200 and SDR104 Command Timeout Window Too Small                                                                                                                          | Yes | Yes                        | Yes |  |

| MSMC          | i2021 — MSMC: Non-Coherent Memory Access to Coherent Memory Can Cause<br>Invalidation of Snoop Filter                                                                                     |     |                            | Yes |  |

|               | i2068 — MSMC: SW considerations for HW data coherency due to inconsistent views of memory                                                                                                 |     |                            | Yes |  |

|               | i2116 — MSMC: Set-hazarding logic withholding RT access waiting on NRT access completion                                                                                                  | Yes | Yes                        | Yes |  |

|               | i2149 — MSMC: MSMC Scrubber Only Targets Bottom 16 of 32 Ways of SRAM/L3\$                                                                                                                | Yes | Yes                        | Yes |  |

|               | i2187 — MSMC: Cache Resize to 0 Refreshes Tags instead of Updating them                                                                                                                   | Yes | Yes                        | Yes |  |

| On-chip Debug | i2013 — On-Chip Debug: The Assertion of Warm Reset Coinciding with a Debug<br>Configuration Access Targeting the STM Subsystem May Result in a Hang of Said Debug<br>Configuration Access | Yes | Yes                        | Yes |  |

|               | i2015 — On-Chip Debug: CPTracer Bus Probes MAIN_CAL0_0 and MCU_SRAM_SLV_1 are not able to Distinguish between Secure and Non-secure Transactions                                          | Yes | Yes                        | Yes |  |

| OSPI          | i2115 — OSPI: OSPI Boot Doesn't Support Some xSPI Modes or xSPI Devices                                                                                                                   | Yes | Yes                        | Yes |  |

|               | i2189 — OSPI: Controller PHY Tuning Algorithm                                                                                                                                             | Yes | Yes                        | Yes |  |

|               | i2249 — OSPI: Internal PHY Loopback and Internal Pad Loopback clocking modes with DDR timing inoperable                                                                                   | Yes | Yes                        | Yes |  |

| PCle          | i2037 — PCIe: PCI-Express May Corrupt Inbound Data                                                                                                                                        |     |                            | Yes |  |

|               | i2046 — PCIE: Failure to link up in Root Complex mode when automatic lane reversal is performed by downstream port                                                                        | Yes | Yes                        | Yes |  |

|               | i2076 — PCIe: QoS support for outbound transactions across PCIe is not fully functional                                                                                                   |     |                            | Yes |  |

|               | i2104 — PCIe: GEN3 (8GT/s) Operation Not Supported                                                                                                                                        | Yes | Yes                        | Yes |  |

|               | 2014 — PCIe: PCIE1 instance does not support outbound address translation bypass                                                                                                          | Yes | Yes                        | Yes |  |

## **Advisories Matrix (continued)**

## Advisories Matrix (continued)

|                |                                                                                                                                      |     | SILICON REVISIONS AFFECTED |     |  |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------|-----|----------------------------|-----|--|

| MODULE         | DESCRIPTION                                                                                                                          |     | AM65x                      |     |  |

|                |                                                                                                                                      | 2.1 | 2.0                        | 1.0 |  |

|                | i2040 — PCIe: Root Port does not set the Link Bandwidth Management and Link Autonomous Bandwidth status bits                         | Yes | Yes                        | Yes |  |

|                | i2041 —PCIe: Calculated Negative Round-trip Time Causes Wrong PTM Requester Local time                                               |     |                            | Yes |  |

|                | i2043 —PCIE: Compliance test fails with certain lane reversal and lane polarity inversion conditions when using Enter Compliance bit | Yes | Yes                        | Yes |  |

| RU_ICSSG       | i2106 — PRU_ICSSG: 100Mbit/s MII is not supported when the PRU_ICSSG is operating at frequencies < 250MHz                            | Yes | Yes                        | Yes |  |

|                | i2193 — PRU-ICSSG: Erroneous FDB aging behavior during switch operation with bucket size of 8                                        |     | Yes                        | Yes |  |

| SIL            | i2137 — PSIL: Clock stop operation can result in undefined behavior                                                                  | Yes | Yes                        | Yes |  |

|                | i2138 — PSIL: Configuration accesses and source thread teardowns may cause data corruption                                           | Yes | Yes                        | Yes |  |

| RA             | i2095 — RA: Peek to Tail Returns Wrong Data                                                                                          | Yes | Yes                        | Yes |  |

| R5FSS          | i2118 — R5FSS: Debug Access in Lock-Step Mode May Result in Failure                                                                  | Yes | Yes                        | Yes |  |

|                | i2161 — Debugger Cannot Access VIM Module While It Is Active                                                                         | Yes | Yes                        | Yes |  |

|                | i2162 — R5FSS: The Same Interrupt Cannot be Nested Back-2-Back Within Another<br>Interrupt                                           | Yes | Yes                        | Yes |  |

|                | i2164 — R5FSS: Errors in ECC injection logic are not detected because the pending interrupts are tied low                            |     | Yes                        | Yes |  |

|                | i2165 — R5FSS: Access to CPU1 TCMs hangs in Lockstep mode                                                                            |     |                            | Yes |  |

| RINGACC, UDMA  | i2023 — RINGACC, UDMA: RINGACC and UDMA Ring State Interoperability Issue after<br>Channel Teardown                                  |     |                            | Yes |  |

| RINGACC        | i2054 — RINGACC: Reads from GCFG Region Can Cause Spurious RAM ECC Errors                                                            |     |                            | Yes |  |

|                | i2177 — RINGACC: The ring accelerator's debug transaction trace stream can be corrupted by certain ring access sequences             | Yes | Yes                        | Yes |  |

| SA2_UL         | i2098 — SA2_UL: Auth/Decrypt Operations with 2nd Input Thread Does Not Send the DMA Packet Out                                       |     |                            | Yes |  |

| Safety Modules | i2103 — Safety Modules: Incorrect Reporting of ECC_GRP, ECC_BIT and ECC_TYPE<br>Information for Functional Safety Errors             | Yes | Yes                        | Yes |  |

| JART           | i2096 — UART: Spurious UART Interrupts When Using DMA                                                                                | Yes | Yes                        | Yes |  |

|                | i2310 — USART: Erroneous clear/trigger of timeout interrupt                                                                          | Yes | Yes                        | Yes |  |

|                | i2311 — USART: Spurious DMA Interrupts                                                                                               | Yes | Yes                        | Yes |  |

| JDMA-P         | i2004 — UDMA-P: UDMA-P Host Packet Descriptor's "0x3FFFFF" Packet Length Mode not Functional                                         |     |                            | Yes |  |

|                | i2163 — UDMA-P: UDMA transfers with ICNTs and/or src/dst addr NOT aligned to 64B fail when used in "event trigger" mode              | Yes | Yes                        | Yes |  |

|                | i2006 — UDMA-P: UDMA-P Real-Time Remote Peer Registers not Functional Across<br>UDMA-P Domains                                       |     |                            | Yes |  |

|                | i2055 — UDMAP: Packet Mode Descriptor Address Space Select Field Restrictions                                                        |     |                            | Yes |  |

|                | i2143 — UDMAP: TX Channel SA2UL teardown issue                                                                                       | Yes | Yes                        | Yes |  |

|                | i2146 — UDMA: Force teardown bitfield readback is masked in realtime TX/RX registers                                                 | Yes | Yes                        | Yes |  |

|                | i2234 — UDMA: TR15 hangs if ICNT0 is less than 64 bytes                                                                              | Yes | Yes                        | Yes |  |

|                | i2320 — UDMA, UDMAP, BCDMA, PKTDMA: Descriptors and TRs required to be returned unfragmented                                         | Yes | Yes                        | Yes |  |

| JSB2PHY        | i2075 — USB2PHY: USB2PHY Charger Detect is Enabled by Default Without VBUS Presence                                                  |     |                            | Yes |  |

| JSB3SS         | i2028 — USB3SS: SuperSpeed USB Non-Functional                                                                                        | Yes | Yes                        | Yes |  |

| /TM            | i2053 — VTM: Software Reads from On-Die Temperature Sensors Can Be Corrupted                                                         |     |                            | Yes |  |

|                | i2145 — VTM: Enabled interrupt event status registers incorrectly return raw unmasked values                                         | Yes | Yes                        | Yes |  |

# 2 Nomenclature, Package Symbolization, and Revision Identification 2.1 Device and Development-Support Tool Nomenclature

To designate the stages in the product development cycle, TI assigns prefixes to the part numbers of all microprocessors (MPUs) and support tools. Each device has one of three prefixes: X, P, or null (no prefix) (for example, AM6546). Texas Instruments recommends two of three possible prefix designators for its support tools: TMDX and TMDS. These prefixes represent evolutionary stages of product development from engineering prototypes (TMDX) through fully qualified production devices and tools (TMDS).

Device development evolutionary flow:

- **X** Experimental device that is not necessarily representative of the final device's electrical specifications and may not use production assembly flow.

- **P** Prototype device that is not necessarily the final silicon die and may not necessarily meet final electrical specifications.

null Production version of the silicon die that is fully qualified.

Support tool development evolutionary flow:

TMDX Development-support product that has not yet completed Texas Instruments internal qualification testing.

TMDS Fully-qualified development-support product.

X and P devices and TMDX development-support tools are shipped against the following disclaimer:

"Developmental product is intended for internal evaluation purposes."

Production devices and TMDS development-support tools have been characterized fully, and the quality and reliability of the device have been demonstrated fully. TI's standard warranty applies.

Predictions show that prototype devices (X or P) have a greater failure rate than the standard production devices. Texas Instruments recommends that these devices not be used in any production system because their expected end-use failure rate still is undefined. Only qualified production devices are to be used.

For additional information how to read the complete device name for any AM654x and AM652x devices, see the specific-device Datasheet (SPRSP08, SPRSP31).

# 2.2 Devices Supported

This document supports the following devices:

- AM6526

- AM6528

- AM6546

- AM6548

# 2.3 Package Symbolization and Revision Identification

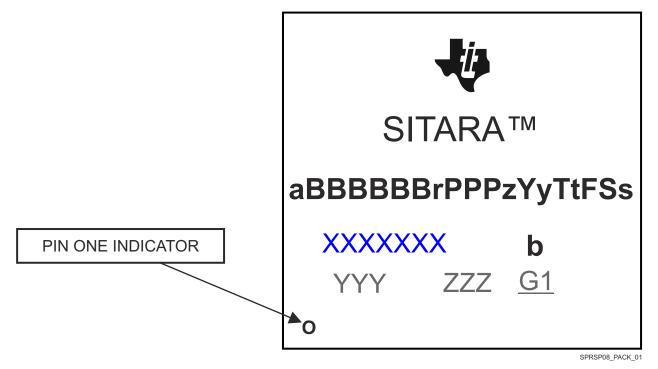

Figure 2-1 shows an example of package symbolization.

Table 2-1 lists the device revision codes.

Figure 2-1. Package Symbolization

| Table 2-1 | Revision   | Identification |

|-----------|------------|----------------|

|           | 1164131011 | Incluincation  |

| DEVICE REVISION CODE | SILICON REVISION | COMMENTS           |

|----------------------|------------------|--------------------|

| BLANK                | 1.0              | Available as null. |

| A                    | 2.0              |                    |

| В                    | 2.1              |                    |

# 3 Silicon Revision 2.1, 2.0, 1.0 Usage Notes and Advisories

This section lists the usage notes and advisories for this silicon revision.

#### 3.1 Silicon Revision 2.1, 2.0, 1.0 Usage Notes

#### 3.1.1 Fail-Safe IO's: Latch-up Risk on Fail-Safe IOs

AM65x silicon revision 1.0, 2.0, and 2.1 incorporate fail-safe I/O's on several pins (I2C0\_SCL, I2C0\_SDA, I2C1\_SCL, I2C1\_SDA, and NMIn). The fail safe I/O's tolerate voltage applied on the pins before their respective I/O supply voltage is ramped up. There is a potential latch up risk based on design reviews of the fail-safe I/O pins when driven high during functional mode. This latch-up risk is not yet confirmed through silicon characterization. To avoid the risk of a latch-up condition, the following steps should be implemented, depending on the mux mode used on the fail safe I/O. If the fail safe I/O is used in an I2C mux mode, then an external pull-up resistor (> 1 kOhm) is required on the signal. If the fail safe I/O is used in any other mux mode, then an external series resistor (> 1 kOhm) should be placed on this signal (close to the SoC).

#### 3.1.2 ADC: High Input Leakage Current May Impact ADC Accuracy

On AM65x silicon revision 1.0, ADC input leakage current may be higher than expected at worst case Process/Voltage/Temperature (PVT) conditions, where process variation and operating temperature are the major contributors. Leakage current is larger for strong process devices operating at elevated temperatures.

There is also a dependency on the potential applied to an ADC input. Leakage current flows out of the ADC when applying a potential equal to VSS, flows into the ADC when applying a potential equal to VDDA\_ADC\_MCU, and the direction change occurs at approximately 42% of VDDA\_ADC\_MCU. Magnitude of leakage current has a non-linear function to the applied potential, where it increases exponentially as the applied potential approached VSS or VDDA\_ADC\_MCU.

Significant error can be introduced in ADC measurements when high impedance sources are connected to inputs with high leakage. This occurs because the input leakage current introduces a voltage drop across the source impedance. For example, the ADC would measure a potential of 1.45 V when measuring a 1.5 V source with 1 k $\Omega$  output impedance that is connected to an ADC input with 50  $\mu$ A of leakage flowing into the ADC input. The error of this measurement would be 50 mV, which is 3.3% lower than the expected value. Reducing the source impedance from 1 k $\Omega$  to 100  $\Omega$  in this example would reduce the measurement error to 0.33%.

There are design techniques that can be used to minimize the impact of input leakage.

Reduce impedance of sources connected to ADC inputs. For example, it may be necessary to buffer outputs of a high impedance sources with voltage-follower operational amplifier circuits.

Design static DC sources to apply a nominal potential of approximately 42% of VDDA\_ADC\_MCU. For example, this approach can be used to minimize leakage when monitoring a DC power source via a resistor voltage divider.

#### 3.1.3 INTRTR: Spurious Interrupts Generated when Programming Certain Interrupt Routers

On AM65x silicon revision 1.0, 2.0, and 2.1, programming the MUXCNTL\_n registers to configure input-output mapping of interrupt signals may result in a short glitch on the intended output signal, causing a spurious interrupt. Additionally, reprogramming the register to the same value may also cause a glitch.

The *Interrupt Routers* section in the device TRM also describes this behavior, which is applicable to multiple Interrupt Routers (INTRTR) instantiated in the device, including:

- WKUP\_GPIOMUX\_INTRTR0

- GPIO\_INTRTR0

- MAIN2MCU\_LVL\_INTRTR0

- MAIN2MCU\_PLS\_INTRTR0

- TIMESYNC\_INTRTR0

- CMPEVT\_INTRTR0

To prevent system from servicing these spurious interrupts unintentionally, following programming sequence are recommended when configuring INTR interrupt mapping.

**In systems where interrupt mapping is static**, typically with RTOS or bare-metal programming, the following interrupt configuration sequence shall be followed:

- 1. Disable interrupt at GIC and VIM for the interrupt sourced from the INTRTR output;

- 2. Re-configure MUXCNTL\_n on the specific INTRTR;

- 3. Clear spurious interrupt if any by clearing raw status;

- 4. Enable the interrupt at GIC and/or VIM.

**In systems where static interrupt configurations not possible**, such as Linux systems with standard GIC drivers, interrupt drivers must detect false interrupt caused by the glitch, and clear the false interrupt. This method can be performed by the following programming sequence:

- If possible to customize interrupt handler, the handler shall first clear any interrupts before the handler being initialized, otherwise,

- The handler must check the interrupt source (such as GPIO status) to check valid event exists, then service the interrupt.

**In systems with shared IRQs** where multiple INTRTRs map to the same GIC IRQ, the following pseudo code may be used for the global interrupt handler:

isr(irq)

{ if (!read\_status\_reg()) return IRQ\_NONE; }

In this case, each ISR can check and report to global IRQ handler that it wasn't the cause of IRQ, allowing the global IRQ handler to call the next handler in the list for that IRQ. In case of spurious IRQ, all the handlers (if there are no events) will return IRQ\_NONE, which means Linux kernel will report a spurious IRQ on that line as the global handler will report EOI.

i2351 OSPI: Controller does not support Continuous Read mode with NAND Flash

The SoC and OSPI controller doesn't support Continuous Read mode with NAND Flash since the OSPI controller can deassert the CSn signal (by design intent) to the Flash memory between internal DMA bus requests to the OSPI controller.

The issue occurs because "Continuous Read" mode offered by some OSPI/QSPI NAND Flash memories requires the Chip Select input to remain asserted for an entire burst transaction.

The SoC internal DMA controllers and other initiators are limited to 1023 B or smaller transactions, and arbitration/queuing can happen both inside of the various DMA controllers or in the interconnect between any DMA controller and the OSPI peripheral. This results in delays in bus requests to the OSPI controller that result in the external CSn signal being deasserted.

NOR Flash memories are not affected by CSn de-assertion and Continuous Read mode works as expected.

Workaround(s): Software should use page/buffered read modes to access NAND flash.

# 3.2 Silicon Revision 2.1, 2.0, 1.0 Advisories

3.2.1 Silicon Revision 2.1, 2.0, 1.0 Advisory List

8

**Details:**

| i939       | MCAN: Message Transmitted with Wrong Arbitration and Control Fields (Early Start of Frame)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Details    | The erratum is limited to the case when MCAN is in state "Receiver" (MCAN_PSR[4:3]<br>ACT = "10") with no pending transmission (no MCAN_TXBRP bit set) and a new<br>transmission is requested before the 3rd bit of Intermission is reached and this 3rd bit<br>of intermission is seen dominant. This issue occurs only with disturbed CAN bus.                                                                                                                                                                                                                                                                                                                                                                              |

|            | <ul> <li>Under the following conditions, a message with wrong ID, format, and DLC is transmitted:</li> <li>MCAN is in state "Receiver" (MCAN_PSR[4:3] ACT = "10"), no pending transmission</li> <li>A new transmission is requested before the 3rd bit of Intermission is reached</li> <li>The CAN bus is sampled dominant at the third bit of Intermission which is treated as SoF (see ISO11898-1:2015 Section 10.4.2.2).</li> </ul>                                                                                                                                                                                                                                                                                        |

|            | <ul> <li>Under the conditions listed above, it may happen, that:</li> <li>The shift register is not loaded with ID, format, and DLC of the requested message</li> <li>The MCAN will start arbitration with wrong ID, format, and DLC on the next bit</li> <li>In case the ID wins arbitration, a CAN message with valid CRC is transmitted</li> <li>In case this message is acknowledged, the ID stored in the Tx Event FIFO is the ID of the requested Tx message and not the ID of the message transmitted on the CAN bus, no error is detected by the transmitting MCAN</li> <li>If the message loses arbitration or is disturbed by an error, it is retransmitted with correct arbitration and control fields.</li> </ul> |

| Workaround | Workaround 1:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | Request a new transmission only if another transmission is already pending or when the MCAN is not in state "Receiver" (when MCAN_PSR[4:3] ACT !=, "10").                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|            | <ul> <li>To avoid activating the transmission request in the critical time window between the sample points of the 2nd and 3rd bit of Intermission, following can be done:</li> <li>Evaluate the Rx Interrupt flags MCAN_IR[19] DRX, MCAN_IR[0] RF0N, MCAN_IR[4] RF1N which are set at the last bit of EoF when a received and accepted message gets valid. Prevent the transmission of any message within 3 bit times after detecting the Rx interrupt flags.</li> </ul>                                                                                                                                                                                                                                                     |

|            | Workaround 2:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | A checksum covering arbitration and control fields can be added to the data field of the message to be transmitted, to detect frames transmitted with wrong arbitration and control fields.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|            | Workaround 3:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | Set MCAN_CCCR[0] INIT bit, add transmission request for the message and then clear MCAN_CCCR[0] INIT bit. This needs to be done for each message to be transmitted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|            | Workaround 4:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|            | Keep the number of pending transmissions always at ">0" by frequently requesting a message so that the condition "no pending transmission" is never met. The frequently requested message may be given a low priority, losing arbitration to all other messages.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|            | In case, where all the nodes present on the CAN bus have this workaround implemented,<br>at least two nodes shall have this frequently sent low priority message with different<br>priorities/identifiers. Rest of the nodes can have one of these priorities/identifiers (same)<br>as the priority of this frequently sent message.                                                                                                                                                                                                                                                                                                                                                                                          |

Comparison within available Workarounds is shown in Table 3-1.

# i939 (continued) MCAN: Message Transmitted with Wrong Arbitration and Control Fields (Early Start of Frame)

| Table 3-1. Comparison within available Workarounds |                                                                                                                                                                                                                                                           |                                                                                                                                                                                                     |  |

|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Workaround (WA) #                                  | Advantages                                                                                                                                                                                                                                                | Disadvantages                                                                                                                                                                                       |  |

| 1                                                  | <ul> <li>Easy to implement.</li> <li>Fix is only limited to a local node with the erratum.</li> </ul>                                                                                                                                                     | <ul> <li>Only viable in interrupt context.</li> <li>Effectiveness is vastly dependent<br/>on interrupt service latency.</li> <li>Application becomes complicated.</li> </ul>                        |  |

| 2                                                  | • Simple and easy to implement.                                                                                                                                                                                                                           | • All nodes on the bus must<br>implement this WA. Restricting use<br>of device for end points and all the<br>existing nodes needs to be updated<br>to support this WA.                              |  |

| 3                                                  | • Simple and easy to implement.                                                                                                                                                                                                                           | <ul> <li>Node will miss any messages<br/>received during this sequence.</li> <li>System (including existing nodes)<br/>needs to be updated for detecting<br/>the dropped/missed message.</li> </ul> |  |

| 4                                                  | <ul> <li>DMA can be used to send the<br/>frequently sent low priority message<br/>to reduce CPU load.</li> <li>Most effective and viable amongst<br/>available workarounds.</li> <li>Fix is only limited to a local node<br/>with the erratum.</li> </ul> | <ul> <li>100% CAN Bus utilization at all times.</li> <li>Increased CPU load in case CPU is used to send the message.</li> </ul>                                                                     |  |

#### i2000

Revision(s) Affected:

Details:

Table 3-2 lists the pixel data formats that are not supported in the DSS.

DSS: DSS Does Not Support YUV Pixel Data Formats

#### Table 3-2. Unsupported Pixel Data Formats

| Format # |                    | Dixal Formata       | Pipline | support    | Component |

|----------|--------------------|---------------------|---------|------------|-----------|

| Packed   | Planar             | Pixel Formats Video |         | Video_Lite | Bit Depth |

| 0x3E     | N/A <sup>(1)</sup> | YUV422-YUV2         | Х       | Х          | 8/10/12   |

| 0x3F     | N/A                | YUV422-UYVY         | Х       | Х          | 8/10/12   |

| N/A      | 0x3D               | YUV422-NV12         | Х       | Х          | 8/10/12   |

| N/A      | N/A                | YUV422-NV21         | Х       | Х          | 8/10/12   |

(1) N/A - Not Applicable

AM65x SR 1.0

Selecting the above formats (see Table 3-2) along with using the color conversion logic inside Video/Video\_Lite pipeline will result in incorrect color reproduction at the output of DSS.

# **Workaround(s):** Customer may use RGB mode for image capture or configure the input camera to use RGB mode instead of YUV formats referenced above. If RGB mode not available, it is recommended to use processor core or GPU to convert YUV to RGB.

| i2004                    | UDMA-P: UDMA-P Host Packet Descriptor's "0x3FFFFF" Packet Length Mode not<br>Functional                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|--------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision(s)<br>Affected: | AM65x SR 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Details:                 | In the UDMA-P Host Packet Descriptor (PD Word 0), there is a 22-bit packet length field. This field is typically set to a value between $0x0 - 0x3FFFFE$ , representing the total byte length of the packet. If the packet length is less than the sum of the buffer length, the packet will be truncated to the size specified in the packet length field. Specifying a packet length that is greater than the sum of the buffers will result in an error.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                          | Alternatively, the packet length field can be set to a special value, 0x3FFFFF, which disables truncation and allows the UDMA-P to transmit as much data as is specified in the Buffer Length fields. This "0x3FFFF" mode is not functional.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Workaround(s):           | There is no workaround. A valid packet length field must be supplied. This only prevents a user from sending a packet larger than 0x3FFFFE bytes, which is more than large enough for any envisioned use case.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| i2006                    | UDMA-P: UDMA-P Real-Time Remote Peer Registers not Functional Across UDMA-<br>P Domains                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Revision(s)<br>Affected: | AM65x SR 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Details:                 | In the UDMA-P, both RX and TX channels contain a specific set of registers called<br>"Real-time Remote Peer Registers" (UDMA_PEER[0-15]_j registers). These registers<br>provide access to the remote peer device's real time registers within the PSI-L<br>configuration (PSIL_CFG) register space, address 0x400 to 0x40F. The peer device is<br>the device that the UDMA-P channel is communicating with, and is set via the Rx/TX<br>Channel Destination Thread ID Mapping Register (UDMA_THREAD_j register). Once the<br>UDMA_THREAD_j register is configured with the peer's PSI-L thread ID, any access to<br>the UDMA_PEER[0-15]_j registers on the UDMA-P will results in an access to the PSI-L<br>register on the peer corresponding to the offset of the register accessed. For example,<br>peer register 0 maps to peer PSI-L address 0x400, and peer register 1 maps to peer<br>PSI-L address 0x401, and so on. Having these registers allows the UDMA-P driver to<br>access peer registers in the 0x400 to 0x40F range without accessing the configuration<br>proxy IP, which in some environments can be reserved for secure access only. |

|                          | There are two UDMA-P instances on the device. These instances exist in separate domains called MAIN and MCU. Along with the two UDMA-P instances, individual peripheral devices also reside in both domains. It was originally intended that a UDMA-P instance in one domain would seamlessly work with a peripheral in the other domain. For the most part, this is still the case, but when it comes to using the peer registers, a bug in the internal message routing prevents the UDMA-P peer registers in the MAIN domain from accessing the PSI-L registers of a peripheral in the MCU domain, and prevents the UDMA-P peer registers of the peripheral in the MAIN domain. Read results across UDMA-P domains will always be invalid. Writes across UDMA-P domains will still take affect but will take longer than normal.                                                                                                                                                                                                                                                                                                                       |

| Workaround(s):           | Avoid using the UDMA-P peer registers in one domain to access PSI-L registers of a peripheral in the other domain. This can be accomplished in one of two ways:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                          | <ol> <li>Always allocate a TX/RX channel from the UDMA-P residing in the same domain as<br/>the target peripheral.</li> <li>Use the PSI-L proxy module to write PSI-L registers 0x400 through 0x40F instead of<br/>the using the UDMA-P Real-time Remote Peer registers.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| i2006 (continued)        | UDMA-P: UDMA-P Real-Time Remote Peer Registers not Functional Across UDMA-<br>P Domains                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          | Solution 1 avoids the problem by making sure that the peer register access is never performed "across domains."                                                                                                                                                                                                                                                                                                                                                               |

|                          | Solution 2 avoids the problem by not making use of the affected registers. The drawback here is that in some environments the PSI-L proxy module is restricted to secure access only. This means that any register access will have to be done through secure code, increasing overhead.                                                                                                                                                                                      |

|                          | Note, solution 1 is preferred due to secure access limitation for this resource configuration when implementing the workaround in software.                                                                                                                                                                                                                                                                                                                                   |

| i2009                    | DDRSS: DDR Controller ECC Scrubbing Feature Can Cause DRAM Data Corruption                                                                                                                                                                                                                                                                                                                                                                                                    |

| Revision(s)<br>Affected: | AM65x SR 2.1, SR 2.0, SR 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details:                 | The DDR controller implements a built-in ECC scrubbing feature that is used<br>for correcting single-bit errors in the DRAM. When this feature is enabled<br>(DDRCTL_ECCCFG0[4] DIS_SCRUB = 0), the controller schedules an ECC scrub<br>operation when a single-bit error is detected. However, in some cases, the ECC scrub<br>operation can lead to accidental auto-correction of two-bit errors in an another DRAM<br>location, thus corrupting the data inside the DRAM. |

| Workaround(s):           | The ECC scrubbing feature inside the DDR controller must be kept disabled at all times by setting DIS_SCRUB = 1 in the DDR controller's ECC Configuration 0 (DDRCTRL_ECCCFG0) register.                                                                                                                                                                                                                                                                                       |

| i2013                    | On-Chip Debug: The Assertion of Warm Reset Coinciding with a Debug<br>Configuration Access Targeting the STM Subsystem May Result in a Hang of Said<br>Debug Configuration Access                                                                                                                                                                                                                                                                                             |

| Revision(s)<br>Affected: | AM65x SR 2.1, SR 2.0, SR 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details:                 | Debug configuration transaction initiators and targets are typically susceptible only to power-on-resets. The STM Subsystem includes the Arm <sup>®</sup> STM500 and a CoreSight <sup>™</sup> CTI that provides triggering support. The orthogonal debug interconnect for the STM Subsystem is affected by warm reset. This results in the possibility of a hang of a debug configuration access that is active when warm reset is active                                     |

| Workaround(s):           | There is no workaround for this issue. The user needs to be aware of the possibility that a debug configuration hang may result in the rare case that the STM Subsystem is being configured while warm reset is active.                                                                                                                                                                                                                                                       |

| i2015                    | On-Chip Debug: CPTracer Bus Probes MAIN_CAL0_0 and MCU_SRAM_SLV_1 are not able to Distinguish between Secure and Non-secure Transactions                                                                                                                                                                                                                                                                                                                                      |

| Revision(s)<br>Affected: | AM65x SR 2.1, SR 2.0, SR 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Details:                 | The CPTracer Bus Probe supports filtering on the properties of bus transactions including a property 'psecure' that identifies a transaction as being secure or non-secure. In the case of bus probe instances supporting MAIN_CAL0_0 and MCU_SRAM_SLV_1, the 'psecure' property will always indicate that a transaction is non-secure even if it were actually secure.                                                                                                       |

| www.u.com                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|--------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| i2015 (continued)        | On-Chip Debug: CPTracer Bus Probes MAIN_CAL0_0 and MCU_SRAM_SLV_1 are not able to Distinguish between Secure and Non-secure Transactions                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |

| Workaround(s):           | There are no workarounds for this issue. The user needs to be aware that secure and non-secure transactions are not distinguishable for MAIN_CAL0_0 and MCU_SRAM_SLV_1 CPTracer Bus Probes.                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| i2018                    | DCC: Incorrect Counter Values in DCC Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| Revision(s)<br>Affected: | AM65x SR 1.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| Details:                 | Due to a potential race condition, if the DCCCNT0, DCCCNT1, DCCCNTSEED0,<br>or DCCCNTSEED1 registers are modified while a DCC module is in operation or<br>immediately before a DCC module is put in to operation, the counter may not expire<br>correctly as per the programmed counter value (expiring either late or early). This could<br>result in an incorrect error signal value, indicating either a false pass or fail.                                                                                                                                                                     |  |  |  |