# WHITE PAPER

Punya Prakash, Product Marketing Manager, Sitara™ processors

> Kazunobu Shin, Systems Engineer, Sitara™ processors Texas Instruments

Texas Instruments

# Power optimization techniques for energyefficient systems

## Building blocks of a power-efficient system

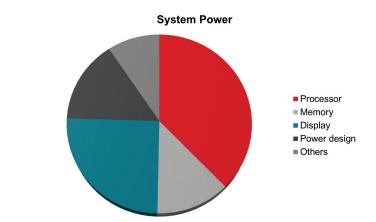

Several techniques can be implemented to reduce active and static power consumption. Typically the highest impact on power consumption is due to four key components – the processor, DDR memory, display and power design, as shown by Figure 1. Power optimization can be achieved by selecting the right system components and designing dynamic software architecture.

*Figure 1: Power consumption of various key system components. This figure assumes 85 percent power design efficiency, DDR3 memory and active display.*

#### Processor

TI's Sitara AM335x processors provide highly flexible power management architecture. Depending on the application, the processor and core can be adapted to take advantage of the best performance and power configuration.

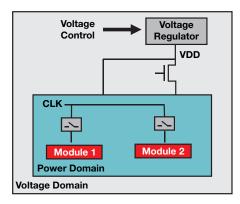

The power, reset and clock management (PRCM) module, shown in Figure 2, and the Linux<sup>™</sup> power management software stack can be used to optimize AM335x processor power. This minimizes power consumption of the processor since it aids control of the core

## Introduction

Advancement in technology has aided progression of automation and control systems that provide a cohesive operation of various mechanical, electronics and lighting systems. Apart from offering a convenient lifestyle, these solutions play an essential role in energy monitoring. These solutions require diligent understanding and optimization of complete systems.

While each solution has a common goal of energy conservation, they have completely different system requirements. The Texas Instruments (TI) Sitara<sup>™</sup> processor solutions offer the flexibility to design applicationspecific systems. The latest Sitara AM335x processors provide a scalable architecture with speed ranging from 300MHz to 1GHz. In addition to the scalable frequency, pinto-pin compatible devices enable customers to innovate and develop a highly flexible and comprehensive range of solutions.

This white paper will outline system choices and their impact on the system power. It will provide a comprehensive overview of the processor power management features and discuss the key contributors to the overall system power. modules. Voltage domain is critical in controlling different operating performance points (OPP). OPP is a combination of processor voltage and frequency that can be controlled by the user for optimal processor power for any given performance requirement.

The voltage control and the voltage regulator are external and enabled through a power management IC (PMIC). While the system is active, individual power domain(s) and all its modules can be turned off. Similarly, specific modules can also be controlled. While one module is functional, another could be completely turned off when not in use.

Figure 2: PRCM architecture.

TI's Sitara AM335x processors support separate voltage domains for MPU and CORE. By having different voltage domains, MPU and CORE OPPs can be configured and controlled independently.

Depending on the application requirement, the MPU OPP can be dynamically changed. The AM335x processors support five different operating points: OPP50, OPP100, OPP120, Turbo and Nitro. With a wide frequency range of 10MHz to 1GHz, it provides flexible configuration. Custom processor frequency can be supported with a dedicated processor DPLL. Figure 3 shows MPU voltage and performance at the five different supported OPPs.

The CORE OPP supports two voltage operating points and interconnects frequency sets. Lower CORE OPP can be used for significant power savings provided the bus throughput supported by lower CORE OPP is sufficient for system performance requirements. CORE OPP voltage and performance operating points are shown in Figure 4 on the following page.

| VDD_MPU OPP | VDD_MPU | ARM <sup>®</sup> Cortex™-A8 |

|-------------|---------|-----------------------------|

| Nitro       | 1.325 V | 1 GHz                       |

| Turbo       | 1.26 V  | 800 MHz                     |

| OPP120      | 1.2 V   | 720 MHz                     |

| OPP100      | 1.1 V   | 600 MHz                     |

| OPP50       | 0.95 V  | 300 MHz                     |

| VDD_CORE OPP | VDD_CORE | DDR3, DDR3L | DDR2    | mDDR    | L3 and L4           |

|--------------|----------|-------------|---------|---------|---------------------|

| OPP00        | 1.1 V    | 400 MHz     | 266 MHz | 200 MHz | 200 MHz and 100 MHz |

| OPP50        | 0.95 V   | -           | 125 MHz | 90 MHz  | 100 MHz and 50 MHz  |

Figure 4: CORE operating performance points (OPPs).

#### **DDR memory**

TI's Sitara AM335x processor memory controller supports a breath of DDR memory – LPDDR1, DDR2, DDR3 (L) (RS). While the period of availability for each DDR option is determined by the memory vendor(s), the choice of the memory has an impact of up to 20 percent on the overall system power.

In general, the LPDDR memory has the lowest active and stand-by power. In addition to this, LPDDR and DDR2 memory is supported at OPP50, which reduces the power consumption significantly in active mode when the reduced memory bandwidth is sufficient for applications.

VTT termination is required for better signal integrity in applications where higher DDR speed is essential. This added integrity comes at the cost of some power dissipation. DDR VTT termination can be avoided when single DDR3/DDR3L device is used with the AM335x processor and PCB board is designed by following TI's recommended PCB design guidelines. The **Sitara AM335x processor datasheet** describes the PCB design guidelines to implement this solution.

#### Display

There are several ways a display-based application can be tailored for power optimization. The processor also offers an optional resistive-touch controller and SGX graphics accelerator. Using the AM335x PRCM module, each of these sub-systems could be disabled while not in use.

Applications can be developed to turn off the display panel after a certain duration or through a manual event and could save up to 23 percent of processor power. The display can be re-enabled through external events such as touch or proximity sensor.

In addition to this, the display resolution, refresh rate and brightness of the display can be tweaked to achieve higher system power optimization.

#### **Power design**

TI provides an array of PMIC solutions for the AM335x processor, based on the application requirements. The PMIC solution can be selected to optimize the solution. As shown in Figure 5, each of the PMIC solutions supports a variety of processor frequency and memory configuration. In addition to this, some additional features can directly benefit the system cost of the solution.

|                        | TPS65217x                                         |       |                                        | TPS65910x                             |                 | TPS650250                               |                    |

|------------------------|---------------------------------------------------|-------|----------------------------------------|---------------------------------------|-----------------|-----------------------------------------|--------------------|

|                        | A                                                 | В     | C                                      | D                                     | А               | A3                                      |                    |

| Battery charger        | Yes                                               |       |                                        | No                                    |                 | No                                      |                    |

| Boost                  | WLED backlighting                                 |       |                                        | 5-V boost                             |                 | No                                      |                    |

| AM335x OPP             | OPP50, OPP50, OPP100, OPP120, OPP100 Turbo, Nitro |       | OPP50, OPP100, OPP120,<br>Turbo, Nitro |                                       | OPP50, OPP100   |                                         |                    |

| Power                  | 3 DCDC @ 1.2A<br>4 LD0                            |       |                                        | 2 DCDC @ 1.5A<br>1 DCDC @ 1A<br>9 LDO |                 | 1 DCDC @ 1.6A<br>2 DCDC @ 0.8A<br>3 LDO |                    |

| Input voltage range    | 2.7 – 5.8 V                                       |       |                                        | 2.7 – 5.5 V                           |                 | 2.5 - 6.5 V                             |                    |

| DVFS /<br>SmartReflex™ | Yes                                               |       |                                        | Yes                                   |                 | No                                      |                    |

| RTC-only mode          | Yes                                               |       |                                        | Y                                     | es              | No                                      |                    |

| DDR                    | DDR2, L                                           | PDDR1 | DDR3                                   | DDR3L                                 | DDR2,<br>LPDDR1 | DDR3                                    | DDR2, LPDDR1, DDR3 |

| Package                | 48-pin QFN, 6mm × 6mm                             |       |                                        | 48-pin QFN,                           | 6mm × 6mm       | 32-pin QFN, 5mm × 5mm                   |                    |

| T <sub>A</sub>         | -40°C to 105°C                                    |       |                                        | -40°C                                 | to 85°C         | -40°C to 85°C                           |                    |

Figure 5: TI offers a range of PMIC solutions for TI's Sitara™ AM335x processors.

The TPS65217x supports portable solutions with the integrated battery charger. Backlight for displaybased applications can be supported using this PMIC solution. The TPS65910x provides support from 300MHz – 1GHz and provides advanced power management features such as SmartReflex<sup>™</sup> and RTC mode support aids flexible power management architecture. The third variant, TPS650250, is a simple, low-cost solution that supports OPP50 and OPP100.

There is a trade-off between the board footprint, BOM cost and efficiency when selecting power IC components. The efficiency of the power ICs can impact the system power significantly. Dissipation from the various power IC components could penalize the overall system contributing to the system power consumption. It is challenging to quantify this due to the broad spectrum of applications that have a variety of board cost and size targets. The power IC datasheet provides efficiency curves at certain operating conditions. Understanding efficiency at target input and output voltages and selecting the right DC-DC converter to meet system power consumption target is important to design power-efficient systems.

## Processor power optimization practices

### Power latency trade-off

TI's Sitara AM335x processors offer several deep sleep (DS) modes, which are directly proportional to the power consumption of the core processor. There are several factors which determine the DS mode – period of inactivity, manual over-ride and the active peripherals connected to the core. While the deepest mode, DS0, can provide the lowest core power, it also has to bring longer latency to wake the system. Complementary to the DS mode, the stand-by mode offers faster wake-up latency. Details of each of these power modes are shown in Figure 6 on the following page.

TI's Sitara AM335x processors support five DPLLs, which in turn can support independent frequency control, regulate processor, DDR and display clock frequency based on the application needs. In addition to this, six dual-voltage I/O banks can be configured for 1.8V or 3.3V. The 1.8V I/O will benefit reduction of processor power consumption.

| Power modes | Processor state                                                                                                                                          | Wakeup sources                                                      |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|

| Standby     | All power supplies are ON.<br>Main oscillator is ON.<br>All DPLLs are in bypass.<br>PD_PER and PD_WKUP power domains are ON.<br>DDR is in self-refresh.  | Any GPIO pins                                                       |

| Deepsleep1  | All power supplies are ON.<br>Main oscillator is OFF.<br>All DPLLs are in bypass.<br>PD_PER and PD_WKUP power domains are ON.<br>DDR is in self-refresh. | DeepSleep0 wakeup sources and USB remote signal                     |

| Deepsleep0  | All power supplies are ON.<br>Main oscillator is OFF.<br>All DPLLs are in bypass.<br>Only PD_WKUP power domain is ON.<br>DDR is in self-refresh.         | GPIO0 bank, Timer1, Touch-screen controller, UARTO, I²CO, RTC alarm |

| RTC-only    | RTC timer remains active and all other device functionality is disabled.                                                                                 | RTC alarm, EXT_WAKEUP pin                                           |

Figure 6: DS modes excel + wake source.

The AM335x processor supports various wake sources such as the resistive touch, UARTO, USB or GPIOO with 32 pins. In addition to these, RTC alarm is also supported, which can be used for timer-based wake. Additional information on Texas Instruments' power management architecture is described in TI's white paper on "**Power saving techniques lead to ultra-low-power processors for battery-operated devices**."

# Power-efficient display-based application

In order to provide a better perspective on the various topics discussed here, this section will describe a display-based application optimized for efficient power solution. In this Wi-Fi® enabled application, TI's Sitara AM335x processor is used to process the data aggregated from various end nodes.

If USB and Ethernet sub-systems are not used in this application, using the flexible PRCM architecture these modules can be disabled.

- Data aggregation from various nodes, the end nodes are connected to the processor through I<sup>2</sup>C and Wi-Fi.

- 2. Wi-Fi is connected through SDIO and GPIO is used as the wake source.

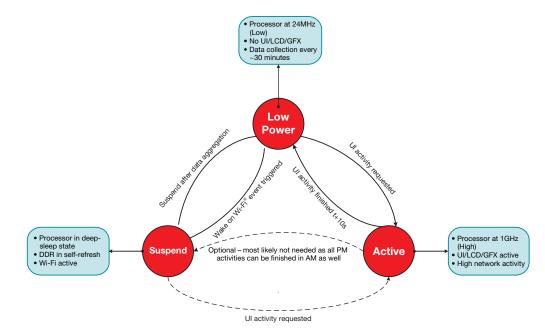

Figure 7: State diagram of example application for optimized power.

The state diagram in Figure 7 depicts system transition from active mode to low-power mode. In active mode, the processor is running at 1GHz and has the display and graphics engine enabled. When the high network activity reduces and there is no user interface (UI) activity for over 10s, the system could transition to a low-power state. The system can be rendered active with any UI activity such as a proximity sensor or touch event.

In low-power mode the display and graphics engine modules are disabled. In addition to turning off the display, the processor frequency can be reduced to as low as 10MHz. After data collection every, say 30 minutes, the processor can be suspended to a deep-sleep state. In suspend state, the DDR is in self-refresh. A Wi-Fi event can wake the processor through a GPIO and restore the processor in low-power mode.

The processor can be suspended to a deep-sleep state from active mode directly; any wake event while in suspend mode will restore the system to active state.

**Conclusions** With rising energy costs, system automation is an increasing trend. Investments in these systems require a scalable solution with low power/performance to high performance. TI's Sitara AM335x processor offers a flexible architecture with high processing capability for computationally intensive applications. With the various power and performance knobs to turn, users can benefit from an intelligent whole product that has been designed for efficiency which provides a competitive advantage.

**Resources** For more information about TI's Sitara AM335x processors, please visit ti.com/am335x.

For more information about power solutions for TI's Sitara AM335x processor, please visit **ti.com/pmic**.

Important Notice: The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

Sitara and SmartReflex are trademarks of Texas Instruments Incorporated. All other trademarks are the property of their respective owners.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2019, Texas Instruments Incorporated