# How anti-aliasing filter design techniques improve active RF converter front ends

#### **Rob Reeder**

Application Manager High-Speed Data Converters

### Introduction

Active analog-to-digital (ADC) front ends using a fully differential amplifier (FDA) can offer a host of advantages, such as better impedance matching, pass-band flatness and signal gain. However, if you require only a portion of the ADC's band for your next design, it might be necessary to use an anti-aliasing filter (AAF) between the output of the FDA and the input of the ADC. An AAF will yield better signal-to-noise (SNR) performance and lower spurious or spurious-free dynamic range (SFDR) within your frequency band requirements.

With any kind of AAF filter constructions, you will have several trade-offs to consider during the implementation process: filter order and topology, or whether you will need back termination or series resistances to enhance the interface between the FDA and the ADC. In this paper, I'll discuss these AAF nuances and how to circumvent any huddles you might encounter in your next design.

# AAF design approach

Assuming that you have decided on the correct FDA for your application and whether to use either a lowpass or band-pass filter in order to achieve optimum performance (bandwidth, SNR and SFDR) in front of the ADC, follow these three steps:

- Understand the amplifier's characterized load impedance (RL). In order for the amplifier to perform at its best, the amplifier should "see" the correct DC load or RL listed in the data sheet for optimum performance. This is the characterized impedance typically found at the top of the specification tables.

- Determine a starting point for the correct amount of output series resistance to use closest to the amplifier's outputs. This helps prevent unwanted peaking in the pass band. You'll also typically find this information in the FDA's data sheet - LMH5401 8-GHz, Low-Noise, Low-Power, Fully-Differential Amplifier Data Sheet.

- Determine whether to use one or more external parallel resistors to back-terminate the input to the ADC, and the starting value of the input series resistance to isolate the ADC from the filter. These series resistors also help reduce unnecessary peaking in the pass band and "kickback" commonly found in unbuffered ADCs.

Figure 1 shows an example of the specification table.

| LMH5401<br>SB0S710D – OCTOBER 2014–REVISED FEBRUARY 2018<br>6.5 Electrical Characteristics: V <sub>s</sub> = 5 V |                                                         |                                                                       |                   |             |            |            |                              |

|------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|-----------------------------------------------------------------------|-------------------|-------------|------------|------------|------------------------------|

| at T <sub>A</sub> =                                                                                              |                                                         | –2.5 V, V <sub>CM</sub> = 0 V, <mark>R<sub>L</sub> = 200-Ω</mark> dif | ferential, G = 12 | dB (4 V/V), | single-end | ded input  | t,                           |

|                                                                                                                  | PARAMETER                                               | TEST CONDITIONS                                                       | MIN               | ТҮР         | МАХ        | UNIT       | TEST<br>LEVEL <sup>(2)</sup> |

| AC PER                                                                                                           | FORMANCE                                                |                                                                       |                   |             |            |            |                              |

|                                                                                                                  |                                                         |                                                                       |                   |             |            |            | -                            |

| GBP                                                                                                              | Gain bandwidth product                                  | G = 30 dB (32 V/V)                                                    |                   | 8           |            | GHz        | С                            |

|                                                                                                                  | Gain bandwidth product<br>Small-signal, –3-dB bandwidth | G = 30 dB (32 V/V)<br>V <sub>O</sub> = 200 mV <sub>PP</sub>           |                   | 6.2         |            | GHz<br>GHz | C<br>C                       |

| GBP<br>SSBW<br>LSBW                                                                                              |                                                         |                                                                       |                   | -           |            |            |                              |

Figure 1. Electrical specification table excerpt from the LMH5401 data sheet, where  $RL = 200\Omega$ .

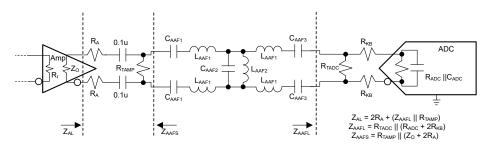

The generalized circuit shown in **Figure 2** and filter parameter list in **Table 1** apply to most high-speed differential FDA and ADC interfaces; you can use both as a basis for the AAF design.

Although not every filter construction will be exactly the same, **Figure 2** can serve as a blueprint on how to kick-start your design. Using this design approach will tend to minimize the insertion loss of the filter by taking advantage of the relatively high input impedance of most high-speed ADCs and the relatively low output impedance of the driving source (the FDA).

Figure 2. Generalized FDA and ADC interface with a band-pass filter.

| Symbol            | Parameter description                                         |  |

|-------------------|---------------------------------------------------------------|--|

| R <sub>i</sub>    | Amplifier input impedance                                     |  |

| Zo                | Amplifier output impedance                                    |  |

| R <sub>A</sub>    | Series output resistance located near the amplifier's outputs |  |

| R <sub>TAMP</sub> | Back-termination resistance near the amplifier outputs        |  |

| C <sub>AAF1</sub> | First AAF capacitor                                           |  |

| L <sub>AAF1</sub> | First AAF inductor                                            |  |

| C <sub>AAF2</sub> | Second AAF capacitor                                          |  |

| L <sub>AAF2</sub> | Second AAF inductor                                           |  |

| C <sub>AAF3</sub> | Third AAF capacitor                                           |  |

| R <sub>TADC</sub> | Back-termination resistance near the ADC inputs               |  |

| R <sub>KB</sub>   | Series kickback resistor located near the ADC's inputs        |  |

| Z <sub>AL</sub>   | Aggregate load impedance as seen by the amplifier             |  |

| Z <sub>AAFS</sub> | Aggregate source impedance of the AAF                         |  |

| Z <sub>AARL</sub> | Aggregate load impedance of the AAF                           |  |

Table 1. Filter parameter definitions.

### AAF design process and parameters

The basic AAF design process and guidelines are:

- Set the external ADC termination resistor (R<sub>TADC</sub>) appropriately. This helps the AAF realize a "real" impedance over its desired frequency response.

- 2. Select  $R_{KB}$  based on experience or the ADC data sheet recommendations; typically, this will be between 5 $\Omega$  and 50 $\Omega$ .

- Use Equation 1 to calculate the filter load impedance so that the aggregate parallel and series combination of R<sub>TADC</sub>, R<sub>KB</sub> and R<sub>ADC</sub> is between 100Ω and 400Ω. See my recommendation in the previous section.

$$Z_{AAFL} - R_{TADC} \parallel (R_{ADC} + 2R_{KB})$$

(1)

- 4. Select the amplifier external series resistor ( $R_A$ ). This is typically between 5 $\Omega$  and 50 $\Omega$ .  $R_A$  helps dampen the amplifier output response and reduce unnecessary peaking in the pass band.

- Use the calculated Z<sub>AAFL</sub> so that the total load seen by the amplifier (Z<sub>AL</sub>) is optimal for the particular differential amplifier chosen. See Step No. 1 above in the AAF Design Approach Section and use Equation 2:

$$Z_{AL} = 2R_A + Z_{AAFL}$$

(2)

Keep in mind that ZAL is the FDA's characterized  $_{RL}$ ; therefore, using too high or too low a value can have an adverse effect on the amplifier's linearity.

Calculate the filter source resistance using Equation

3:

$$Z_{AAFS} = Z_O + 2R_A \tag{3}$$

Using a filter design program, design the filter using the same source and load impedances, if possible, Z<sub>AAFS</sub> and Z<sub>AAFL</sub>. This helps reduce the amount of loss in the filter. Any mismatch between the input/ output impedance has a loss of 10\*log(input Z/output Z). For example, with an input impedance of 50Ω and an output impedance of 200Ω, the loss of the filter is -6.0dB or 10<sup>\*</sup>log(50/200). Also, using a bandwidth that is about 10% more or higher than the desired bandwidth of the application will ensure that the intended bandwidth is covered per the application, and help overcome any second- and third-order parasitic losses unrealized during the filter implementation process.

After running a few preliminary simulations, give the circuit a quick review for the following items:

- The value of C<sub>AAF2 & 3</sub> should be sufficiently big relative to C<sub>ADC</sub>, which minimizes the sensitivity of the filter to variations in C<sub>ADC</sub>.

- The ratio of Z<sub>AAFL</sub> to Z<sub>AAFS</sub> should not be more than 6-to-7, so that the filter is within the limits of most filter tables and design programs. Ideally, they should be the same to minimize loss, but this is not usually possible.

- Try to use a value of C<sub>AAF2</sub> in the few picofarads range to minimize sensitivity to parasitic capacitance and component variations.

- 11. Inductors  $L_{AAF1}$  and  $L_{AAF2}$  should be reasonable values and in the nanohenries range.

- 12. The value of C<sub>AFF2</sub> and L<sub>AAF2</sub> should be reasonable values; select these two parameters to optimize the filter's center frequency. Sometimes circuit simulators can make these values too low or too high. To make these values more reasonable, simply ratio these values with better standard-value components that maintain the same resonant frequency.

- Use 0201 package styles if possible when designing in the gigahertz range to minimize second- and thirdorder parasitic effects that could disrupt the filter character shape or outline.

In some cases, the filter design program may provide more than one unique solution, especially with higherorder filters. Always choose the solution that uses the most reasonable set of component values. For filter configurations that end with a shunt capacitor, take the ADC's internal input capacitance into consideration as well. You may need an iteration or two to set the filter pole and ultimate bandwidth correctly.

## AAF design trade-offs

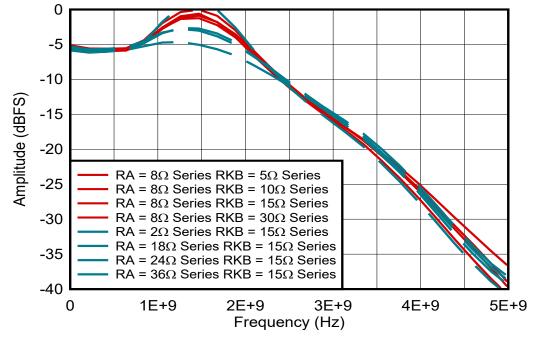

The parameters in this interface circuit are very interactive; therefore, it is almost impossible to optimize the circuit for the primary specifications (bandwidth, bandwidth flatness, SNR, SFDR and gain) without small trade-offs. However, you can minimize bandwidth peaking, which often occurs at the tail end of the bandwidth response, by varying R<sub>A</sub>, R<sub>KB</sub>, or both; either can have a net positive or net negative affect on AAF bandwidth performance.

Notice in **Figure 3** how the pass-band peaking is enhanced or flattened as the value of the FDA's output series resistance ( $R_A$ ) changes (the blue dashed curves). As the value of this resistance decreases, there is more signal peaking, and the amplifier can drive the signal less to fill the ADC's full-scale input range at the cost of the pass-band flatness response near the edge of the AAF frequency response.

Figure 3. Pass-band flatness performance vs. RA and RKB variations.

The value of  $R_A$  could also affect SNR performance. Smaller values, while enhancing bandwidth peaking, tend to decrease the SNR because of the increased bandwidth and unwanted noise.

It's also important to select the  $R_{KB}$  series resistor on the ADC inputs to minimize distortion caused by any residual charge injection from the internal sampling capacitor within the ADC. However, increasing this resistor also tends to enhance or reduce bandwidth peaking as well, depending on the filter topology.

When optimizing for the AAF's rolloff frequency, varying  $C_{AAF2}$  by a small amount allows you to correct for optimal frequency coverage for the application.

Normally, determining the value of the ADC input termination resistor,  $R_{TADC}$ , makes the net ADC input impedance look near typical of most amplifier characteristic load ( $R_L$ ) values. Selecting too high or too low a value for  $R_{TADC}$  can have an adverse effect on the amplifier's linearity, which will then be reflected in the overall SFDR signal-chain lineup.

#### AAF design example

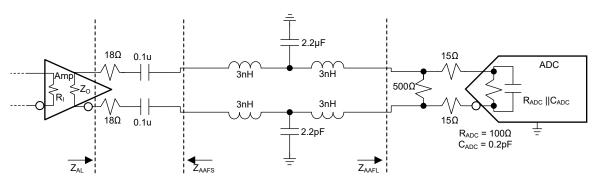

The design example circuit shown in **Figure 4** is a wideband low-pass receiver front end based on the Texas Instruments (TI) **TRF1208**, a 10MHz to 11GHz, 3dB-bandwidth single-ended to differential amplifier and the TI **ADC12DJ5200RF**, a radio frequency (RF) sampling 12-bit dual-channel 5.2GSPS ADC. I optimized the third-order Butterworth AAF based on the performance and interface requirements of the amplifier and ADC; the total insertion loss caused by the filter network and other components was less than 6dB. In this AC-coupled design, the  $0.1\mu$ F capacitors block the common-mode voltages between the amplifier, its termination resistors, and the ADC inputs.

The 10MHz to 11GHz **TRF1208** differential amplifier accepts a single-ended input and converts it to a differential signal operating at a gain of 16dB to compensate for the insertion loss of the filter network, providing an overall signal gain of +7.8dB.

An input signal of –6.8dBm produces a full-scale 800mV peak-to-peak differential signal at the ADC input.

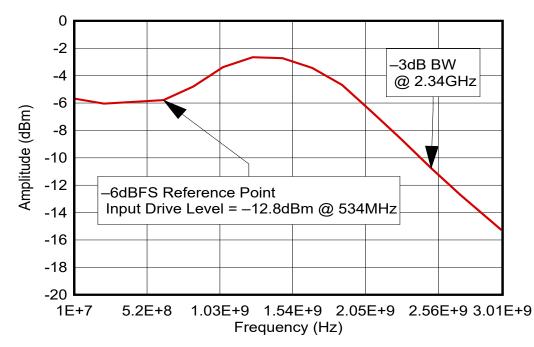

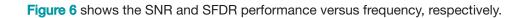

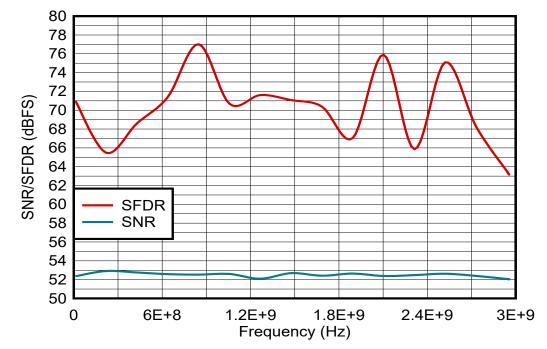

The overall circuit has a bandwidth of 2.34GHz with a pass-band flatness of <3dB. The SNR and SFDR measured with a 534MHz analog input frequency are 52.5dBFS and 71.4dBFS, respectively. The sampling frequency is 5.2GSPS, thereby creating a wideband lowpass filter covering the entire first Nyquist zone between 10MHz and 2.5GHz. Figure 4 shows the values chosen for the final filter passive components (after adjusting for actual circuit parasitics).

The AAF was designed as a third-order Butterworth filter using a standard filter design program with a differential source impedance ( $Z_{AAFS}$ ) of 39 $\Omega$  (2 <sup>'</sup> 18 $\Omega$  + 3 $\Omega$ ), a differential load impedance of 103 $\Omega$  ( $Z_{AAFL}$ ) and a cutoff frequency of 2.4GHz. Because of the higher values of series inductance required in simulation, I decreased these inductors to 3nH in order to account for the inherent trace inductances in the layout and proportionally increased the initial 1.8pF capacitors to ground in the simulations to 2.2pF, thereby helping maintain appropriate rolloff around the 2.4GHz requirement.

The **TRF1208** was not back-terminated in this case in order to achieve net performance, and the net differential impedance load was  $139\Omega$  (Z<sub>AL</sub>). Implementing the  $18\Omega$  series resistors isolated the filter capacitance from the amplifier outputs. For further insight on the FDA's impedances, you candownload the S-parameters.

Installing the  $15\Omega$  resistors in series with the ADC inputs isolated the internal switching transients from the filter and the amplifier, as well as providing the necessary characterized loading to the FDA.

I used the ADC's  $100\Omega$  input impedance per the data sheet. For further insight on the ADC's impedances, **download the S-parameters**.

Figure 4. FDA, AAF, ADC wideband receiver front-end design (simplified schematic).

Table 2 summarizes the measured performance of the system, where the total insertion loss of the network is approximately 5.8dB.

| Performance specs at1dBFS (FS = 0.8V peak to peak), sample rate = | Final results       |  |  |

|-------------------------------------------------------------------|---------------------|--|--|

| 5.2GSPS, JMODE 3                                                  |                     |  |  |

| Cutoff frequency                                                  | 2,340MHz            |  |  |

| Pass-band flatness (10MHz-2.2GHz)                                 | <3.0dB              |  |  |

| SNR full scale at 534MHz                                          | 52.5dBFS            |  |  |

| SFDR at 534MHz                                                    | 71.4dBFS            |  |  |

| H2/H3 at 534MHz                                                   | -71.4dBFS/-73.0dBFS |  |  |

| Overall gain at 534MHz                                            | +7.8dB              |  |  |

| Input drive at 534MHz                                             | -12.8dBm (-6dBFS)   |  |  |

Table 2. Measured performance of the circuit.

Figure 5 shows the resulting combined FDA, AAF and ADC signal chain's frequency response.

Figure 5. Pass-band flatness performance vs. frequency.

Figure 6. SNR/SFDR performance vs. frequency, sample rate = 5.2GSPS.

# AAF design conclusion

Understanding all of the different factors, parameters and trade-offs involved in designing an AAF between an FDA and RF ADC can be more difficult than it seems. The design example described in this article gives each parameter equal weight; therefore, the values chosen represent the interface performance for all of the design characteristics. In some designs, you may choose different values to optimize SFDR, SNR or input drive level depending on system requirements. Keep all of these necessary points in mind so that your next AAF doesn't go resonant.

#### **Additional resources**

- Keysight ADS Simulation

Software: https://www.keysight.com/us/en/

products/software/pathwave-design-software/

pathwave-advanced-design-system.html.

- Ansys/Nuhertz Technologies, Filter Solutions

Design Program: https://www.ansys.com/products/ electronics/ansys-nuhertz-filtersolutions.

- Reeder, Rob. 2022. "Evaluating high-speed RF converter front-end architectures." Planet Analog, April 7, 2022.

- Reeder, Rob. 2022. "A close look at active vs. passive RF converter front-ends." Planet Analog, January 24, 2022.

- Bowick, Chris. 1997. "RF Circuit Design." Boston, Massachusetts: Newnes.

**Important Notice:** The products and services of Texas Instruments Incorporated and its subsidiaries described herein are sold subject to TI's standard terms and conditions of sale. Customers are advised to obtain the most current and complete information about TI products and services before placing orders. TI assumes no liability for applications assistance, customer's applications or product designs, software performance, or infringement of patents. The publication of information regarding any other company's products or services does not constitute TI's approval, warranty or endorsement thereof.

All trademarks are the property of their respective owners.

#### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATA SHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, regulatory or other requirements.

These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

TI objects to and rejects any additional or different terms you may have proposed.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2024, Texas Instruments Incorporated